# LX4580 Data Sheet

**Revision 3.1**

October 11, 2002

Lexra, Inc.

Proprietary and Confidential

DO NOT COPY

COPY NUMBER

LX4580 Data Sheet Revision 3.1 October 11, 2002

Lexra Proprietary and Confidential Copyright © 2002 Lexra, Inc. ALL RIGHTS RESERVED

MIPS and MIPS32 are trademarks and/or registered trademarks of MIPS Technologies, Inc. Other trademarks are the property of their respective owners.

#### DO NOT COPY

•

# **Table of Contents**

## Chapter 1. LX4580 Product Overview

| 1.1.    | Introduction                                               | 1  |

|---------|------------------------------------------------------------|----|

| 1.2.    | Key Features                                               | 2  |

| 1.3.    | Specifications                                             | 3  |

| 1.4.    | LX4580 Architecture                                        | 3  |

|         | 1.4.1. LX4580 CPU                                          | 3  |

|         | 1.4.2. Fine-Grained Hardware Multi-Threading (HMT)         | 4  |

| 1.5.    | Interfaces                                                 | 5  |

| 1.6.    | Software Support                                           | 5  |

|         | 1.6.1. Operating Systems                                   | 5  |

|         | 1.6.2. Development Tools                                   | 5  |

| Chapter | 2. MIPS32 Implementation Specifics                         |    |

| 2.1.    | MIPS32 Implementation Specifics Overview                   | 7  |

| 2.2.    | MIPS32 Instructions                                        | 7  |

|         | 2.2.1. LL/SC                                               | 7  |

|         | 2.2.2. SYNC                                                |    |

|         | 2.2.3. PREF                                                | 8  |

|         | 2.2.4. CACHE                                               | 9  |

|         | 2.2.5. WAIT                                                | 9  |

|         | 2.2.6. Divide (all variants)                               | 9  |

|         | 2.2.7. UDI                                                 | 9  |

| 2.3.    | CP0 Registers                                              | 10 |

| 2.4.    | Interrupts                                                 | 13 |

| 2.5.    | Exceptions                                                 | 14 |

|         | 2.5.1. Reset Context Wait and EJBOOT                       | 15 |

|         | 2.5.2. DM Wait and EJTAG (Debug) Exceptions                | 15 |

| 2.6.    | Address Spaces                                             | 15 |

|         | 2.6.1. Non-Coherence for Different Access Types            | 16 |

| 2.7.    | Endianness                                                 | 16 |

| 2.8.    | EJTAG                                                      | 16 |

| 2.9.    | CP0 Hazards                                                | 17 |

| 2.10.   | Performance Counters                                       | 17 |

| 2.11.   | Release 2 Architecture Support                             | 19 |

|         | 2.11.1. Release 2 Interrupt Modes, Exceptions, Shadow GPRs | 19 |

|         | 2.11.2. Hazard Barrier Instructions                        | 19 |

|         | 2.11.3. Field, Rotate, Shuffle Instructions                |    |

|         | 2.11.4. User Access to Hardware Registers                  |    |

|         | 2.11.5. CP0 Register Changes                               |    |

|         | 2.11.6. 64-bit Coprocessor (FPU)                           | 21 |

|         | 2.11.7. 1KB Pages                                          | 21 |

| Chapter | 3. Reset (RST)                                             |    |

| 3.1.    | Reset Overview                                             | 23 |

| 3.2.    | Reset Distribution                                         | 23 |

| 3.3.    | Reset Operation                                            | 24 |

| 3.4.    | Reset External LX4580 Interfaces                           |    |

|         |                                                            |    |

| Chapter | r 4. LX4580 CPU                                           |    |

|---------|-----------------------------------------------------------|----|

| 4.1.    | LX4580 CPU Overview                                       |    |

| 4.2.    | LX4580 CPU Core                                           |    |

| 4.3.    | Instruction Cache                                         |    |

| 4.4.    |                                                           |    |

| 4.5.    | Cache Line Replacement Algorithm                          |    |

| 4.6.    | CPU Error Handling                                        |    |

|         | 4.6.1. Bus Error Handling (IBE and DBE)                   |    |

|         | 4.6.2. Interrupt Error Response (NMI)                     |    |

| Chapte  | r 5. CBUS_Z Interface (ZBI)                               |    |

| 5.1.    | CBUS_Z Interface Overview                                 |    |

| 5.2.    | CBUS_Z Interface Signal List                              |    |

| 5.3.    | CBUS_Z Endian Mode                                        |    |

| 5.4.    | CBUS_Z Line Read Interleave Order                         |    |

| 5.5.    | CBUS_Z Read Completion                                    |    |

| 5.6.    | CBUS_Z Transaction Types                                  |    |

| 5.7.    | CBUS_Z Protocol                                           |    |

| 5.8.    | CBUS_Z Transaction Timing Diagrams                        |    |

|         | 5.8.1. Back-to-Back Sub-Line Writes with Busy             |    |

|         | 5.8.2. Line Writes                                        |    |

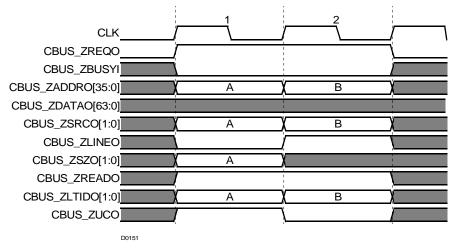

|         | 5.8.3. Read Request                                       |    |

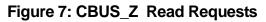

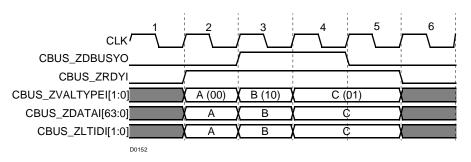

|         | 5.8.4. Returning Read Data                                |    |

| Chapte  | r 6. EC Interface (ECI)                                   |    |

| 6.1.    | Overview                                                  |    |

| 6.2.    | EC Interface Signals                                      |    |

| 6.3.    | EC Interface Endian Mode                                  |    |

| 6.4.    | EC Interface Pending Requests                             |    |

| 6.5.    |                                                           |    |

| 6.6.    |                                                           |    |

| 6.7.    |                                                           |    |

|         | 6.7.1. Consistency of Endian Mode in the System           |    |

|         | 6.7.2. Address Invariance                                 |    |

|         | 6.7.3. Data Invariance                                    |    |

|         | 6.7.4. Reverse Endian Support Not Recommend               |    |

|         | 6.7.5. Endian Mode and Unaligned Load/Store               |    |

| 6.8.    | -                                                         |    |

|         | 6.8.1. CBUS Y Endian Mode                                 |    |

|         | 6.8.2. CBUS_Y Command Encoding                            |    |

|         | 6.8.3. RLE & RLME Eviction Address                        |    |

| 6.9.    |                                                           |    |

|         | 6.9.1. IBUS Header Encoding                               |    |

| 6.10    | ). ECI Actions on CBUS_Y Commands                         |    |

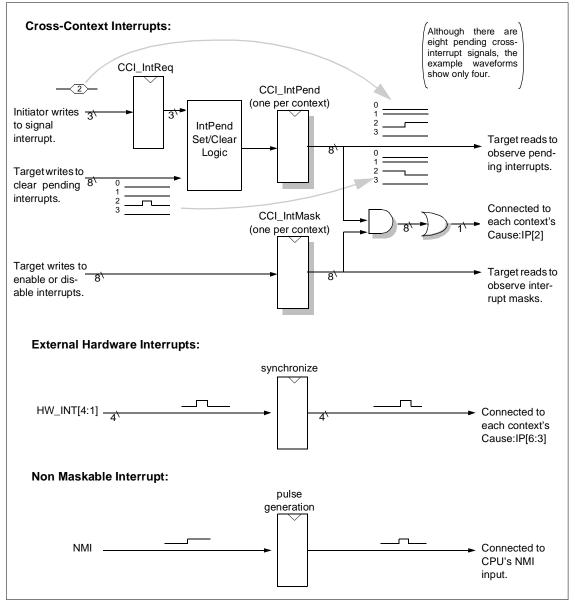

| Chapter | r 7. Interrupts                                           |    |

| 7.1.    | Interrupt Overview                                        |    |

|         | 7.1.1. Cross Context Interrupt Request Register (CCI_Req) |    |

|         | 7.1.2. CCI_IntPend Register (One per context)             |    |

|         | 7.1.3. CCI_IntMask Register (One per context)             |    |

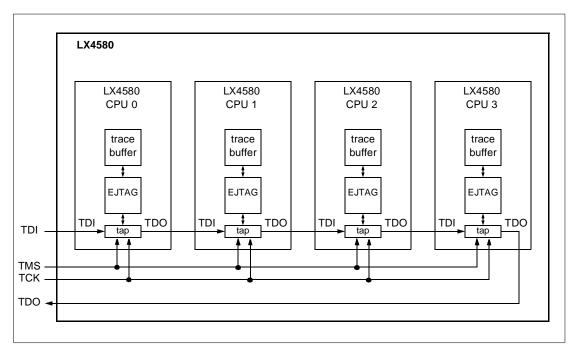

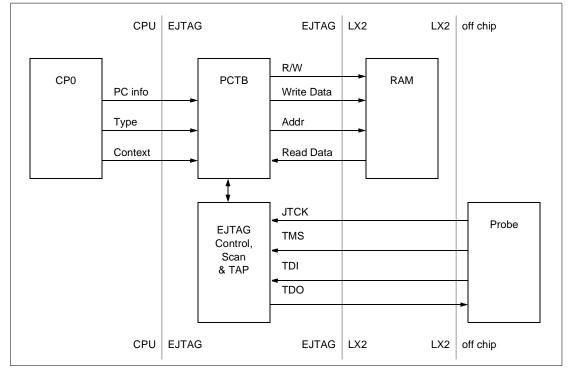

| Chanta  | r 8. EJTAG (EJ)                                           |    |

| 8.1.    |                                                           | 56 |

| 0.1.    |                                                           |    |

|      | 8.1.1.   | EJTAG TAP Registers                                       | 56 |

|------|----------|-----------------------------------------------------------|----|

|      | 8.1.2.   | EJTAG Registers in FF3 (DRSeg)                            | 58 |

| 8.2. | Descrip  | tion of LX4580 CPU Specific EJTAG features                | 59 |

|      | 8.2.1.   | Disable Other Contexts (DOC) EJTAG Control Register bit 6 | 59 |

|      | 8.2.2.   | Context Select (CXS) EJTAG Control Register Bits 30:29    | 59 |

|      | 8.2.3.   | Context in Debug Mode (CDM) EJC Bits 28:27                | 59 |

|      | 8.2.4.   | CNTXUse & CNTX in Breakpoint Control Registers            | 60 |

|      | 8.2.5.   | Precise Data Breaks                                       | 60 |

|      | 8.2.6.   | Data Value Break Loads                                    | 60 |

|      | 8.2.7.   | EJTAG_ADDR (36-bit)                                       | 60 |

|      | 8.2.8.   | PC Trace Buffer & TAC                                     | 60 |

|      | 8.2.9.   | Instruction Replay                                        | 64 |

|      | 8.2.10.  | DMwait                                                    | 64 |

|      | 8.2.11.  | Debug Mode Overrides Disable Context                      | 65 |

|      | 8.2.12.  | EJTAG BOOT                                                | 65 |

|      | 8.2.13.  | The Lexra Probe                                           | 65 |

|      | 8.2.14.  | Access to EJTAG Memory Space                              | 65 |

| nter | 9. Inter | rfaces                                                    |    |

## **Chapter 9. Interfaces**

| 9.1. | Interfaces |  | 67 | 7 |

|------|------------|--|----|---|

|------|------------|--|----|---|

# **List of Figures**

| Figure 1:  | LX4580 Diagram                                |  |

|------------|-----------------------------------------------|--|

| Figure 2:  | Reset Overview                                |  |

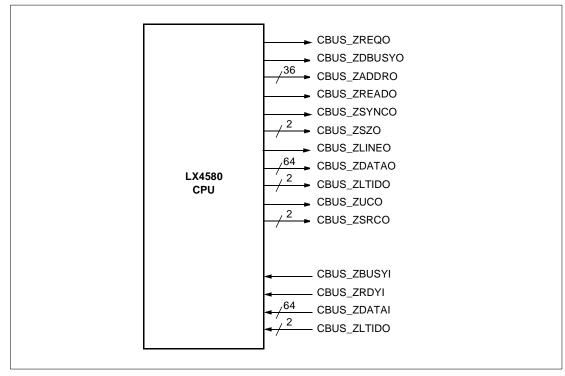

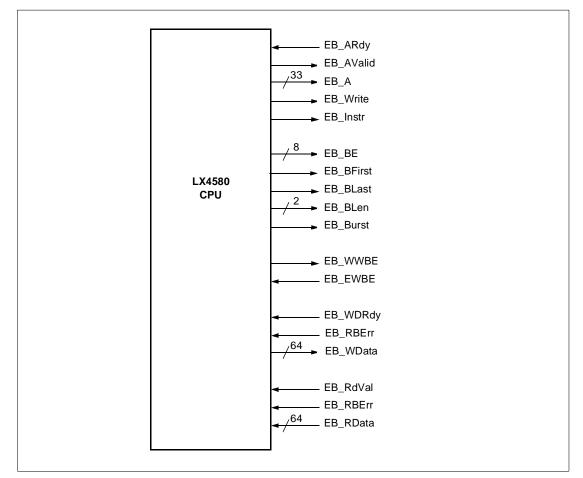

| Figure 3:  | LX4580 CPU and System Interface               |  |

| Figure 4:  | CBUS_Z Interface (ZBI)                        |  |

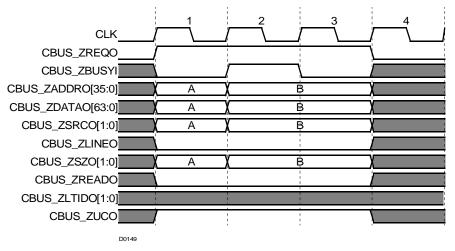

| Figure 5:  | CBUS_Z Back-to-Back Sub-Line Writes with Busy |  |

| Figure 6:  | CBUS_Z Line Write                             |  |

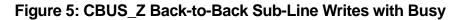

| Figure 7:  | CBUS_Z Read Requests                          |  |

| Figure 8:  | CBUS_Z Sub-Line Read Data and DBUSY           |  |

| Figure 9:  | Read Data for a Line Read Request             |  |

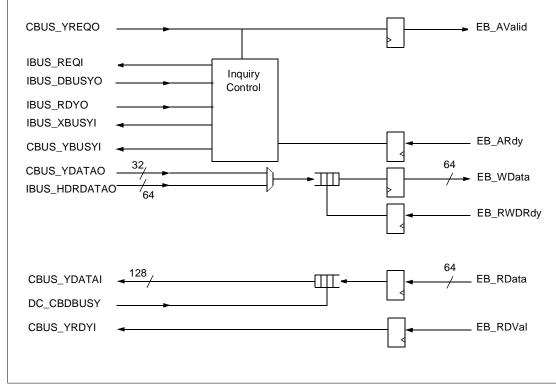

| Figure 10: | EC Interface (ECI)                            |  |

| Figure 11: | EC Interface Gasket (ECI)                     |  |

| Figure 12: | LX4580 Interrupt Logic                        |  |

| Figure 13: | LX4580 ETJAG Organization                     |  |

| Figure 14: | CPU EJTAG Block Diagram                       |  |

# **List of Tables**

| Table 1:  | Summary of LX4580 Interfaces                            | . 5 |

|-----------|---------------------------------------------------------|-----|

| Table 2:  | Standard CP0 Registers                                  | 10  |

| Table 4:  | Interrupt Sources                                       | 13  |

| Table 3:  | Implementation Dependent CP0 Registers                  | 13  |

| Table 5:  | Exception List                                          |     |

| Table 6:  | CntxSel (bits 13:11) Field of PerfCnt Control Registers | 17  |

| Table 7:  | Event Field of PerfCnt Control Registers                | 17  |

| Table 8:  | Hardware Register Values                                | 20  |

| Table 9:  | Reset External Interface                                | 24  |

| Table 10: | Cache Line Replacement Algorithm                        | 26  |

| Table 11: | CBUS_Z Signal List                                      | 29  |

| Table 12: | Effect of Endian Mode on CBUS_Z                         | 31  |

| Table 13: | EC Interface Signals                                    | 38  |

| Table 14: | Effect of Endian Mode on EC Interface                   | 39  |

| Table 15: | Supported Configurations                                | 41  |

| Table 16: | Big Endian Unaligned Load/Store Address Adjustments     | 43  |

| Table 17: | Little Endian Unaligned Load/Store Address Adjustments  | 44  |

| Table 18: | CBUS_Y Request Interface                                | 44  |

| Table 19: | CBUS Reply Interface                                    |     |

| Table 20: | Effect of Endian Mode on CBUS_Y                         | 45  |

| Table 21: | CBUS_Y Commands                                         | 46  |

| Table 22: | CBUS_Y Source Encoding                                  | 47  |

| Table 23: | CBUS_Y Destination Encoding                             | 47  |

| Table 24: | CBUS_Y Reply Encoding                                   | 47  |

| Table 25: | IBUS Request Interface                                  | 48  |

| Table 26: | IBUS Reply Interface                                    |     |

| Table 27: | IBUS Commands                                           | 48  |

| Table 28: | ECI Actions on CBUS_Y Requests                          |     |

| Table 29: | ECI Actions on IBUS Replies                             | 49  |

| Table 30: | EJTAG TAP Registers                                     | 56  |

| Table 31: | EJTAG DRSeg Registers                                   | 58  |

| Table 32: | COP0 EJTAG registers                                    | 59  |

| Table 33: | Interface Summary                                       | 67  |

## 1.1. Introduction

The LX4580, designed to support Lexra's family of network communication ICs, is the highest performance MIPS32<sup>TM</sup> processor optimized for "High-Touch" packet processing applications. Based on Lexra's 3rd generation 7-stage pipeline, the LX4580 is able to achieve 3x the performance of other 32-bit CPU platforms.

Enabling this technology break-through is Lexra's innovative fine-grained Hardware Multi-Threading (HMT). HMT dramatically improves system performance by its ability to alternate the execution of four hardware threads. The processor stays 100% utilized even while multiple threads are servicing cache misses. From a system perspective, the LX4580 overcomes the fundamental bottleneck to application performance - memory latency.

Additional benefits due to HMT are an increase in pipeline efficiency as well as removal of timing-critical forwarding paths. Stalls due to load-to-use are typically eliminated while commonly used features like branch prediction are altogether no longer needed. Collectively this results in die area saving and an increase in processor performance.

The LX4580 includes features like the Coprocessor Interface (CI) and User Defined Instruction (UDI) interface are used to specialize the processor to the target application.

The LX4580 supports the new MIPS32<sup>™</sup> Release 2.0 ISA to leverage a rich legacy of tools, application software, and operating systems available for the MIPS architecture. With its optional Memory Management Unit (MMU) the LX4580 supports Linux<sup>®</sup> SMP running on the hardware threads, in single and multiprocessor systems.

Software views the LX4580 as four virtual CPUs or hardware threads running in parallel. Cache coherency is maintained for data accesses among the multiple contexts. Applications using concurrent kernel threads or user processes will run on the LX4580 virtually unchanged while taking full advantage of HMT. Alternatively, a single threaded RTOS such as VxWorks® can run on one thread while other threads function as coprocessors.

The LX4580 CPU provides the ultimate in both performance and flexibility required to execute demanding high touch applications. The LX4580 CPU implements the MIPS32<sup>™</sup> ISA, with additional specialized instructions for optimized packet processing. Peak processor performance is 700 Dhrystone 2.1 MIPS. The CPU incorporates Lexra's innovative fine-grained Hardware Multi-Threading (HMT) technology. As a result, high CPU performance can be sustained even while L1 cache misses are serviced.

The CPU includes a 64-bit MIPS EC<sup>tm</sup> interface for connection to main memory and other peripherals. This interface provides access to a wide range of SoC interconnect and modules such as DRAM controllers, PCI and AMBA bridges and custom I/O interfaces. The optional CBUS interface provides an easy to use but powerful alternative for connection to proprietary or third party buses.

Target applications for the LX4580 include:

#### • Enterprise Security Systems

These systems provide specialized services such as VPN, firewall and intrusion detection for traffic between the enterprise LAN or data center and WAN. The LX4580 can be used for either Linux-based application services or for "front-end" network processing in these systems.

#### Web Appliances

Typical products include Switches, Web Directors, Web Caches. The LX4580 provides consolidated functionality with strong Layer 4-7 decision making for policy and contentbase load balancing, security, session and site persistence based on HTTP cookies, IP address, etc.

I

#### Network Attached Storage (NAS) Servers

New generation NAS Servers provide remote storage-on-demand while lowering administration costs and leverage the learning curve of 3rd party internet technology. The LX4580 provides TCP termination, iSCSI protocol conversion and security services.

#### 1.2. Key Features

Processor

- 7-stage execution pipeline

- MIPS32<sup>TM</sup> Release 2.0 ISA

- Specialized instructions for packet processing

- Lexra ISA extensions:

- Hash with key size 4 to 24 bits

- Dual 16-bit ones-complement add

- Fine-grained Hardware Multi-Threading (HMT)

- Four hardware threads of execution

- Unique register set, interrupts and TLB per thread

Local Memory Interface

- Up to 64 KB L1 Instruction Cache

- Up to 64 KB L1 Data Cache

- 4-way set associative

- Configurable cache line size (16, 32, 64 and 128 bytes)

- Conforms to MESI coherency protocol

- Write-through or write-back Data Cache

- Up to 1 MB fixed local instruction/data memory

System Bus Interface

- Optional CBUS or EC interfaces

- Split transaction (CBUS) or pipelined (EC)

- 64-bit data-path

- Multi-master support

- Burst mode

Memory Management Unit (MMU)

- 4 KB page size

- Supports 36-bit physical addresses

- 2-entry ITLB, 4-entry DTLB, 24-entry JTLB (per thread)

Multiply-Accumulate Unit (MAC)

• Two-cycle 32x32b multiply, multiply-accumulate

Enhanced JTAG (EJTAG) 2.0.0 Debug

- Single-stepping

- Address and data breakpoints

- Full-speed real-time PC trace

- Supports multi-processor debug

User Defined Instructions (UDI)

- Application-specific ALU instruction extensions

- Supports 3-register operand and 2-register/immediate formats

Coprocessors

• An application-specific coprocessor can be attached to the Coprocessor Interface (CI)

#### 1.3. Specifications

- Technology: 0.13µm CMOS

- 500 MHz Processor Clock (worst-case)

- 3.8 mm<sup>2</sup>Core Area

- 360 mW Power (worst-case)

- Operating Temperature: 125° C junction

- Supply Voltage: 1.2 V nominal

## 1.4. LX4580 Architecture

#### 1.4.1. LX4580 CPU

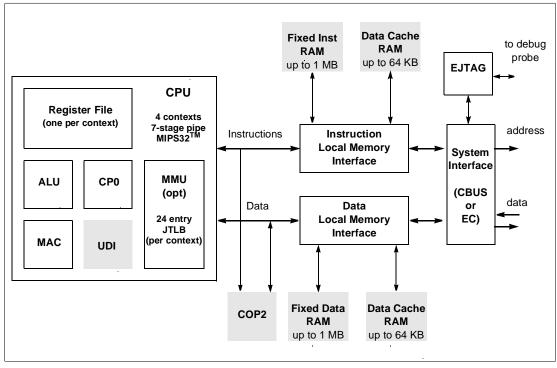

The LX4580 incorporates four (4) LX4580 CPUs, illustrated in Figure 1. The LX4580 is a complete RISC processor subsystem, optimized for high-performance packet processing.

## Figure 1: LX4580 Diagram

The major blocks are the Register file and ALU (RALU), Coprocessor 0 (CP0), the local memory interfaces (LMI) to up to 64KB instruction cache and 6K4B data cache.

I

I

Lexra's LX4580 CPU implements the full Release 2 MIPS32<sup>TM</sup> instruction set. The MIPS32 *optional* and *recommended* features included in the CPU are detailed in Chapter 2. A number of implementation-specific issues are also documented in Chapter 2. Lexra has extended the MIPS32 ISA with additional instructions for optimized packet processing. These instructions are described in Chapter 2. The CPU includes an MMU and support 36-bit physical addresses.

The CPU execution pipeline is 7-stage and exclusively uses the rising edge of the processor clock. The 7stage pipeline permits a full cycle for address register to data output register for both instruction cache read and data cache read. As a result the CPU pipeline achieves maximum performance for its implementation technology and methodology and will readily port to future technologies.

## 1.4.2. Fine-Grained Hardware Multi-Threading (HMT)

The LX4580 CPU incorporates Lexra's proprietary implementation of *fine-grained Hardware Multi-Threading (HMT)*. Although HMT is transparent to software it provides significant performance advantages to the LX4580 customer that deserve attention in this overview.

In Lexra's implementation, instructions are issued round-robin from four alternate contexts. Each context has an independent program counter and general register file. Other software visible state is also replicated as detailed in Chapter 2. In the absence of an L1 cache miss, the four contexts support four independent execution threads.

In typical network processing programs data cache miss rates are high and a single-threaded processor is idle much of the time. The problem can be mitigated somewhat with a second level cache, offering faster service time than main memory. However, in Lexra's implementation of HMT, as few as two active threads can maintain 100% CPU utilization while cache misses from the other two threads are being served.

Additional performance benefits from HMT result from the following:

- All timing-critical internal forwarding paths are eliminated. As a result, for a specific technology and design methodology, high processor clock speed is achieved.

- Branch prediction is not required. There are sufficient cycles between issue slots so that branch outcome can be correctly resolved without prediction. Other high-end RISC architectures have devoted significant silicon area and power to minimizing stalls from branch prediction failures.

- Load-to-use delay is minimized. The 7-stage pipeline would normally require two load-touse delay cycles. With HMT, the load-to-use delay is zero or one cycle depending on the number of actively executing threads. As a result, the frequency of load interlock stalls is reduced.

Lexra's simulations indicate that if 3% of instructions cause an cache miss, HMT delivers a 3X performance benefit compared to a similar single issue CPU. This performance benefit can be realized in applications with sufficient thread parallelism. Assigning each thread one or more independent packet flows allows HMT to be fully exploited in the LX4580 target applications.

4

## 1.5. Interfaces

Table 1 summarizes the interfaces provided by the LX4580.

| Name                                              | Qty | Performance         | Function                                                                                                                      |

|---------------------------------------------------|-----|---------------------|-------------------------------------------------------------------------------------------------------------------------------|

| EC Interface <sup>a</sup>                         | 1   | 500 MHz (CPU clock) | Interface option to system devices. See<br>Chapter 6 and MIPS "EC <sup>tm</sup> Interface Speci-<br>fication", Revision 1.05. |

| CBUS Interface <sup>a</sup> 1 500 MHz (CPU clock) |     | 500 MHz (CPU clock) | Interface option to system devices. See<br>Chapter 5.                                                                         |

| CI                                                | 1   | 500 MHz (CPU clock) | Coprocessor interface (COP2). See XREF.                                                                                       |

| UDI                                               | 1   | 500 MHz (CPU clock) | User Defined Instructions. See XREF.                                                                                          |

| EJTAG                                             | 1   | 40 MHz clock.       | Scan chain debug.<br>Conforms to EJTAG 2.0.<br>Provides PC-trace. Multi-processor support.                                    |

Table 1: Summary of LX4580 Interfaces

a. RTL is configurable to support EC interface or CBUS interface.

## 1.6. Software Support

## 1.6.1. Operating Systems

Two operating systems are provided for the LX4580:

- Linux<sup>®</sup>, version 2.4 and higher, with full SMP support running on all CPUs and hardware threads. Full source code for the Linux<sup>®</sup> kernel is available from MontaVista<sup>TM</sup> and the Hardware Abstraction Layer is available from Lexra and MontaVista<sup>TM</sup>.

- VxWorks® version 5.4 running on one thread. The Hardware Abstraction Layer is available from Wind River.

## 1.6.2. Development Tools

Extensive On-Chip Debug Features

- EJTAG

- Performance Counters

Complete Development Platform

- C/C++ development tool chain

- Development board

- Device drivers and abstraction layer

- Sample code

## 2.1. MIPS32 Implementation Specifics Overview

The MIPS32 architecture defines certain features as optional (or recommended), in which case they may be completely omitted from a compliant implementation. Other MIPS32 features are defined as implementation dependent, in which case one or more choices must be supported for compliance. Finally there are optional extensions that an implementation may provide.

The purpose of this chapter is to detail the implementation dependent features of the LX4580 CPU. The specifics of each of the following areas is discussed in its own section:

- Instructions

- CP0 Registers

- Interrupts

- Exceptions

- Address Spaces

- Endianness

- EJTAG

- CP0 Hazards

- Release 2 Features

#### 2.2. MIPS32 Instructions

This section describes implementation specific details of the following MIPS32 instructions:

- LL/SC

- SYNC

- PREF

- CACHE

- WAIT

- Divide (all variants)

- UDI

## 2.2.1. LL/SC

The unit of memory that is used to determine whether the SC should fail is one cache line. That is, after the LL, a write to any byte in the line by any other entity will cause the SC to fail. In addition:

- Any load, store or CACHE instruction between the LL and the SC by the same context, when not in debug mode, will cause the SC to fail.

- Any ERET between the LL and SC by the same context will cause the SC to fail.

- Any store to the cache line by a different context in the same CPU between the LL and SC will cause the SC to fail.

- A load or store between the LL and the SC by the same context in debug mode, may cause the SC to fail in rare instances. The precise conditions are described below.

The remaining implementation of this feature relies solely on the state of the cache line within the L1 data cache in the CPU as follows:

| On LL, if cache miss, request line Shared      |           |

|------------------------------------------------|-----------|

| else line is already Shared or Modified (okay) |           |

|                                                |           |

| On SC, if dcache miss                          | SC fails  |

| else if already Modified                       | SC passes |

| else request line upgrade to Modified          |           |

| if invalidated before request completes        | SC fails  |

| else                                           | SC passes |

|                                                |           |

Note that there is no architecturally visible CP0 LLAddr register.

For HMT, a variant of the LLAddr register (just the data cache Way and Index) is used for two purposes:

- Another context is not allowed to cause a replacement eviction of the line between the LL and SC. To prevent this, the particular data cache Way and Index (of the line used by the LL) are saved while the SC is pending or until it is guaranteed to fail, whichever comes first.

- Another context in the processor can store to the line, forcing the SC to fail. This is detected by the L1 data cache using the saved Way and Index.

- If all four contexts have a pending SC for the same Index (each to a different Way), then no Way of that Index is available for replacement eviction. Any load or store by any context that is not in debug mode, will enable a Way for eviction without impacting the other contexts because it can cause its own context SC to fail. However, a load or store in debug mode that requires a replacement eviction in the same Index will use the saved Way of the context that is executing in debug mode. This rare case will also cause the SC to fail for the context in question.

#### 2.2.2. SYNC

There is only one outstanding data cache miss (for either loads or stores) at a time for each context.

An uncached load prevents further progress by a context until the load data returns.

Therefore all cached loads/stores and uncached loads are strongly ordered for any given context.

To cover the ordering of uncached stores, SYNC flushes uncached stores previously executed by the same context, preventing forward progress by context executing the SYNC until all such stores are Acked by their targets.

#### 2.2.3. PREF

The instruction is treated as NOP.

## 2.2.4. CACHE

The following operations are supported:

- I Index Invalidate

- D Index WritebackInvalidate / Index Invalidate

- I,D Index Store Tag

- I,D Hit Invalidate

- D Hit WritebackInvalidate / Hit Invalidate

- D Hit Writeback

The following are not implemented:

- S,T anything

- I Fill

- I,D Index Load Tag

- I,D Fetch and Lock (there are no Locks in instruction or data cache)

Since the instruction and data caches are shared by all four contexts in the CPU, it is the responsibility of software to avoid conflicting CACHE instruction execution. Note that the Data cache Writeback operations and the Instruction cache Invalidate operations are generally safe across contexts since they do not discard potentially modified data. If the Store Tag operation is only used for initialization, that too should be safe to use. Finally, the Data cache Hit Invalidate should be used with caution since it discards data that may have been written by a context different than the one executing the CACHE instruction.

#### 2.2.5. WAIT

Only Code 0 is supported.

When the WAIT instruction is executed by a context in the LX4580 CPU, that context is suspended from further execution. The only way to restart a context after completion of a WAIT instruction is with an enabled interrupt to that context. The EPC will point to the instruction after the WAIT.

Since the other contexts continue execution, the WAIT instruction does not cause the CPU clocks to stop nor are the CPU caches disabled. Any power savings from the WAIT instruction would be on a gate-level basis in that reduced pipeline activity would reduce the circuit switching current. The primary benefit of the WAIT instruction is to reduce contention among contexts for the CPU pipeline slots while one or more contexts are merely waiting for some external event. For this reason it is preferred to a software spin loop.

## 2.2.6. Divide (all variants)

The divider detects when the dividend has leading zeroes, reducing its latency in such cases.

#### 2.2.7. UDI

The following User Defined Instructions are implemented:

• HASH rd, rt, keysize

Hash to Key. The 5-bit keysize is a value k in the range 4-24. The 32 source bits contained in rt are hashed to form a key of k bits which is stored in rd[k-1:0]. The remaining bits of rd are zeroed. If k is not in the range 4-24, the results are unpredictable.

Format: 31:26 011100 (Special2), 25:11 zero,rt,rd, 10:6 keysize - 1, 5:0 110000 (Hash)

#### • ACS2 rd, rs, rt

Dual Add for Checksum. This instruction performs dual 16-bit ones complement addition. Considering all quantities as unsigned 16-bit integers, add rs[15:0] to rt[15:0] and independently add rs[31:16] to rt[31:16]. For each addition if there is a carry out of the most significant bit of its result, add one to that result to form its final result. The final results are stored in rd[15:0] and rd[31:16]

Format: 31:26 011100 (Special2), 25:11 rs,rt,rd, 10:6 zero, 5:0 110001 (Acs2)

#### 2.3. CP0 Registers

This section describes implementation specific details of the CP0 registers. In Table 2 each of the standard (MIPS32 Release 2) CP0 registers is listed, together with an indication if the register is not implemented. If it is implemented there may be details on how the implementation handles certain fields in the register. For registers that are implemented, the column labeled HMT indicates whether it is implemented independently for each context (4) or just once per CPU (1). In Table 3, the implemented independently for each context under HMT except CVSTag and CXCtrl (although in CXCtrl the context bits in the CPUNum field are in fact unique by context).

| Name       | Num | Sel | НМТ | Field | Implementation Specific Information            |

|------------|-----|-----|-----|-------|------------------------------------------------|

| Index      | 0   | 0   | 4   |       | 6-bits                                         |

| Random     | 1   | 0   | 4   |       | see note <sup>a</sup>                          |

| EntryLo0,1 | 2,3 | 0   | 4   |       |                                                |

|            |     |     |     | PFN   | 36-bit PA supported                            |

|            |     |     |     | С     | only values 2 or 3 supported                   |

| Context    | 4   | 0   | 4   |       |                                                |

| PageMask   | 5   | 0   | 4   |       | only 4KB and 64MB pages, see note <sup>b</sup> |

|            |     |     |     | MaskX | always 2#11 (no 1KB pages)                     |

| PageGrain  | 5   | 1   |     |       | not implemented                                |

| Wired      | 6   | 0   | 4   |       |                                                |

| HWREna     | 7   | 0   | 4   |       |                                                |

| BadVAddr   | 8   | 0   | 4   |       |                                                |

| Count      | 9   | 0   | 1   |       | counts cpu clocks                              |

| EntryHi    | 10  | 0   | 4   |       |                                                |

| Compare    | 11  | 0   | 4   |       |                                                |

**Table 2: Standard CP0 Registers**

I

| Name   | Num | Sel | нмт | Field       | Implementation Specific Information          |

|--------|-----|-----|-----|-------------|----------------------------------------------|

| Status | 12  | 0   | 4   |             |                                              |

|        |     |     |     | CU321       | always 0 (no FPU, no coprocessors)           |

|        |     |     |     | RE          | always 0 (no ReverseEndian)                  |

|        |     |     |     | RP,FR,MX,PX | always 0                                     |

|        |     |     |     | TS          | always 0                                     |

|        |     |     |     | SR          | always 0                                     |

|        |     |     |     | Impl        | always 0                                     |

|        |     |     |     | KX,SX,UX    | always 0                                     |

|        |     |     |     | R0          | always 0                                     |

| IntCtl | 12  | 1   | 4   |             |                                              |

|        |     |     |     | IPTI        | always 7 (Timer interrupt in IP7)            |

|        |     |     |     | IPPCI       | always 7 (PerfCnt interrupt in IP7)          |

|        |     |     |     | EIC, VS     | always 0                                     |

| SRSCtl | 12  | 2   | 1   |             | always 0                                     |

| SRSMap | 12  | 3   |     |             | not implemented                              |

| Cause  | 13  | 0   | 4   |             |                                              |

|        |     |     |     | DC          | all contexts must set this to stop Count     |

|        |     |     |     | WP          | always 0                                     |

|        |     |     |     | ExcCode     | see note <sup>c</sup>                        |

| EPC    | 14  | 0   | 4   |             |                                              |

| PRId   | 15  | 0   | 1   |             | (lx4580): 0x000bd101                         |

| EBase  | 15  | 1   | 4   |             |                                              |

|        |     |     |     | CPUNum      | same value as CXCtrl.CPUNum                  |

| Config | 16  | 0   | 4   |             |                                              |

| -      |     |     |     | М           | 1                                            |

|        |     |     |     | BE          | reset to 1 or 0 per config pin               |

|        |     |     |     | KU,K23      | value 3 (for Fixed Mapping Table, when MT=3) |

|        |     |     |     | AT          | always 0                                     |

|        |     |     |     | AR          | always 1                                     |

|        |     |     |     | MT          | reset to 1 or 3 per config pin               |

|        |     |     |     | VI          | always 0                                     |

|        |     |     |     | К0          | reset to 2, may be written values 2 or 3     |

## Table 2: Standard CP0 Registers (Continued)

I

I

| Name     | Num | Sel | НМТ | Field    | Implementation Specific Information                           |

|----------|-----|-----|-----|----------|---------------------------------------------------------------|

| Config1  | 16  | 1   | 1   |          |                                                               |

|          |     |     |     | М        | 0                                                             |

|          |     |     |     | MMU-1    | (24 entry) 23                                                 |

|          |     |     |     | IS,IL,IA | 64-byte linesize, 64KB or 32KB or 16KB<br>Icache size, 4 ways |

|          |     |     |     | DS,DL,DA | 64-byte linesize, 64KB or 32KB or 16KB<br>Dcache size,4 ways  |

|          |     |     |     | C2,MD    | always 0                                                      |

|          |     |     |     | PC       | 1                                                             |

|          |     |     |     | WR,CA    | always 0                                                      |

|          |     |     |     | EP       | 1                                                             |

|          |     |     |     | FP       | always 0                                                      |

| Config2  | 16  | 2   |     |          | not implemented                                               |

| Config3  | 16  | 3   |     |          | not implemented                                               |

| LLAddr   | 17  | 0   |     |          | not implemented                                               |

| WatchLo  | 18  |     |     |          | not implemented                                               |

| WatchHi  | 19  |     |     |          | not implemented                                               |

| Debug    | 23  | 0   | 4   |          |                                                               |

| DEPC     | 24  | 0   | 4   |          |                                                               |

| PerfCnt  | 25  | 0-7 | 1   |          | 4 counters with controls.<br>See Section 2.10                 |

| ErrCtl   | 26  | 0   | 1   |          | not implemented                                               |

| CacheErr | 27  |     | 1   |          | not implemented                                               |

| TagLo    | 28  | 0,2 | 1   |          | always 0                                                      |

| DataLo   | 28  | 1,3 |     |          | not implemented                                               |

| TagHi    | 29  | 0,2 |     |          | always 0                                                      |

| DataHi   | 29  | 1,3 |     |          | not implemented                                               |

| ErrorEPC | 30  | 0   | 4   |          |                                                               |

| DESAVE   | 31  | 0   | 1   |          |                                                               |

a. The Random register is decremented on every instruction completion. The two most recently used values by TLBWR in a TLBRefill exception are saved, and are never used in a subsequent TLBWR. TBD: an LFSR is used to further control the decrement of Random.

- b. Only bits 26:25 of the Mask field in the PageMask register are implemented. Writing ones to these bits signifies a 64MB page. All other bit positions return zeroes on reads.

- c. The Cause register ExcCode field can have the following values: Int, Mod, TLBL, TLBS, AdEL, AdES, IBE, DBE, Sys, Bp, RI, CpU, OV, Tr, CacheErr.

The Cause register ExcCode can never have the following values: FPE, C2E, MDMX, WATCH, MCheck.

| Name   | Num | Sel | Bits  | Field  | Implementation Specific Information     |

|--------|-----|-----|-------|--------|-----------------------------------------|

| CXCtrl | 16  | 6   |       |        |                                         |

|        |     |     | 31    | CXTaS  | Test and Set bit. Is set to 1 after any |

|        |     |     |       |        | read <sup>a</sup>                       |

|        |     |     | 30:24 |        | 0                                       |

|        |     |     | 23:16 | SW     | Software usable Read/Write field        |

|        |     |     | 15:12 |        | 0                                       |

|        |     |     | 11:8  | DC3:0  | Disable context in this CPU             |

|        |     |     | 7:5   |        | 0                                       |

|        |     |     | 4:0   | CPUNum | Same as EBASE.CPUNum <sup>a</sup>       |

| CVSTag | 16  | 7   |       |        |                                         |

|        |     |     | 31:0  | CVSTag | ReadOnly for Lexra Internal Use         |

#### **Table 3: Implementation Dependent CP0 Registers**

a. The CXTaS bit allows atomic updates to the remaining fields of the CXCtrl register. A context which reads this bit as one, should not update any fields. A context which reads this bit as zero should restore it to zero whether or not it updates other fields.

The CPUNum is a chip-wide unique identifier for the current thread of execution. The two least significant bits are the context number within the CPU. This value is also readable from the CPUNum field of the EBase CP0 register that is defined by MIPS32 Release 2 or, if enabled in User mode, using the Release 2 RDHWR instruction specifying the CPUNum hardware register. Using those other methods of obtaining CPUNum avoids the need to check and possibly clear CXTaS.

## 2.4. Interrupts

The MIPS32 architecture defines eight interrupts, which are visible as the interrupt pending bits IP7:0 in the CP0 Cause register. In Table 4 the source of each of these pending interrupts is indicated.

| Interrupt | Definition | Generation                                                       |  |

|-----------|------------|------------------------------------------------------------------|--|

| IP0       | Software 0 | Write to Cause IP0                                               |  |

| IP1       | Software 1 | Write to Cause IP1                                               |  |

| IP2       | Hardware 0 | CPU cross context interrupts (See Section 4.2.3)                 |  |

| IP3       | Hardware 1 | External interrupts (See Section 4.2.1)                          |  |

| IP4       | Hardware 2 | External interrupts (See Section 4.2.1)                          |  |

| IP5       | Hardware 3 | External interrupts (See Section 4.2.1)                          |  |

| IP6       | Hardware 4 | External interrupts (See Section 4.2.1)                          |  |

| IP7       | Hardware 5 | Logically OR Timer interrupt with Performance Counter interrupt. |  |

## **Table 4: Interrupt Sources**

## 2.5. Exceptions

All of the exceptions that are defined by the MIPS32 architecture are in Table 5. The relevant implementation specific aspects are indicated.

| Exception                   |        | Implementation Specifics                                                                                   |

|-----------------------------|--------|------------------------------------------------------------------------------------------------------------|

| Reset                       |        |                                                                                                            |

| SoftReset                   |        | implemented like Reset                                                                                     |

| Debug SingleStep            |        |                                                                                                            |

| Debug Interrupt             |        |                                                                                                            |

| Imprecise                   |        | Loads with address+data match                                                                              |

| DebugDataBreak              |        | not implemented                                                                                            |

| NMI                         |        | External input pin                                                                                         |

| MachineCheck                |        | not implemented                                                                                            |

| Interrupt                   |        | see Section 2.4, "Interrupts"                                                                              |

| Deferred Watch              |        | not implemented                                                                                            |

| Debug<br>InstructionBreak   |        |                                                                                                            |

| Watch                       | lfetch | not implemented                                                                                            |

| Address Error               | lfetch |                                                                                                            |

| TLB Refill                  | lfetch |                                                                                                            |

| TLB Invalid                 | lfetch |                                                                                                            |

| Cache Error                 | lfetch | not implemented                                                                                            |

| Bus Error                   | lfetch |                                                                                                            |

| SDBBP                       |        |                                                                                                            |

| Coproc Unusable             |        |                                                                                                            |

| Reserved Inst               |        |                                                                                                            |

| Execution<br>Exception      |        | Overflow, Trap, BREAK, SYSCALL                                                                             |

| Precise Debug<br>DataBreak1 |        | Loads with address match only. All stores                                                                  |

| Watch                       |        | not implemented                                                                                            |

| Address Error               | Data   |                                                                                                            |

| TLB Refill                  | Data   |                                                                                                            |

| TLB Invalid                 | Data   |                                                                                                            |

| TLB Modified                | Data   |                                                                                                            |

| Cache Error                 | Data   | not implemented                                                                                            |

| Bus Error                   | Data   |                                                                                                            |

| Precise Debug<br>DataBreak2 |        | not implemented (Loads with address+data match are always treated as Imprecise Debug DataBreak exceptions) |

## Table 5: Exception List

I

I

## 2.5.1. Reset Context Wait and EJBOOT

When the CPU is reset, only Context 0 is enabled. This is accomplished by the hardware initializing the value of the DC bits in the CXCTRL register so that all contexts other than 0 are disabled. It is the responsibility of the Reset handler that runs in Context 0 to enable the other contexts by clearing their DC bits. When its DC bit is cleared, each of the other contexts will begin execution of the Reset handler. As indicated in Table 2 each context has its own ErrorEPC (used to "return" from the reset exception) and each context can control where it begins execution after it completes the Reset handler.

As described in Section 3.3, the CPU can optionally begin execution at the time of reset by fetching instructions in debug mode from the EJTAG probe. From the CPU point of view, this functionality is similar to the EJBOOT feature of EJTAG 2.5. The extensions to EJTAG 2.0 that control this feature are described in Chapter 8. As in the case of all Reset exceptions, only Context 0 begins execution. Hence only Context 0 enters debug mode in this case. The other contexts begin execution at the standard Reset exception vector in normal mode after their DC bits are cleared.

## 2.5.2. DM Wait and EJTAG (Debug) Exceptions

The LX4580 CPU implements a DM Wait feature which prevents more than one context from executing in Debug mode at any given time. As noted in Table 2 there is only one instance of various CPO registers (such as DESAVE) used to support Debug mode. Furthermore, the EJTAG probe software is unlikely to support intermixed accesses to the Dmseg and Drseg regions. Therefore, after one context begins executing in Debug Mode (due to an EJTAG exception) any other context which takes an EJTAG exception is placed in the DM Wait queue. While in the DM Wait state, the context does not issue any instructions. When the first context leaves Debug Mode (by executing a DERET instruction), the next context in the DM Wait queue resumes execution (in the EJTAG exception handler).

Furthermore, the EJTAG implementation for the LX4580 CPU has an additional feature which optionally allows an EJTAG exception in one context to immediately place all other contexts in the CPU into the DM Wait queue, suspending their execution. When the first context leaves Debug Mode (by executing its DERET), the other contexts resume execution (at whatever point they were suspended). This feature allows the EJTAG probe software to gain control of the entire CPU without needing to put all contexts into Debug Mode simultaneously.

An additional feature of the LX4580 CPU to be noted is that Debug Mode for a context overrides the DC bit for that context. This allows the EJTAG probe to force a context to enter Debug Mode (using the DINT EJTAG exception) even if the context is disabled for normal execution. It also prevents a context that is executing in Debug Mode from being disabled by another context, which could hang the EJTAG probe.

#### 2.6. Address Spaces

Supervisor Mode is not supported.

Kseg2 is supported (instead of Ksseg).

36 Physical Address bits are supported.

The only Memory access types supported are values 2 (uncached) and 3 (cacheable).

Kseg0 can be either uncached or cacheable according to the K0 field of the CP0 Config register.

When the ERL field of the CP0 Status register has value 1, Kuseg is an unmapped, uncached segment and all  $2^{*31}$  bytes are translated. This is the situation upon reset.

As noted in the CP0 Config register MT field, at reset, the TLB can be disabled in which case the Fixed Mapping Table will be used. In this case, as noted in the CP0 Config register KU,K23 field definitions, kuseg, kseg2 and kseg3 will always be cacheable (field value 3).

## 2.6.1. Non-Coherence for Different Access Types

The MIPS32 architecture specifies that results of loads or stores to a location using one memory access type that follow loads or stores to the same location using a different memory access type are unpredictable in general. The architecture states that an implementation specific sequence can enforce coherence between such accesses. For the LX4580 CPU, the only two access types are cacheable and uncached. By performing a CACHE instruction with the Hit Writeback Invalidate operation between the accesses, the coherence can be enforced. The address used for the CACHE instruction may have either the cacheable or uncached access type. This implies that the required CACHE instruction may use the address from either of the accesses so that it can be done immediately after the first access or immediately before the second access, in either case using the same base register and offset as the access in question.

#### 2.7. Endianness

At reset BigEndian or LittleEndian is selected via an external configuration pin.

Reverse endianness is not supported. In MIPS32 Release 2 the WSBH instruction can be used when endian swap is needed. See Section 2.11.3.

#### 2.8. EJTAG

The CPU generally supports the EJTAG 2.0 specification in a manner consistent with the MIPS32 architecture. The exceptions to this are in the following areas:

- PC Trace

- Data Break Exceptions

- HMT Extensions

For PC Trace, the EJTAG 2.0 concept of external trace signals is not supported. This is due to the higher speed of the CPU and the multi-context nature of the LX4580 CPU pipeline. Instead, an on-chip trace buffer is used to capture information about instruction execution. The controls for the trace buffer allow tracing of a single context or tracing of all contexts of the LX4580 CPU simultaneously. The trace buffer and associated controls are described Section 8.2.8.

For Debug Data Break exceptions, the CPU implements the concept of Precise Data Breaks that is defined in the EJTAG 2.5 specification. In particular, for Loads, only the address match applies. For Stores, both the address and data match (if enabled) apply. Imprecise Data Breaks, which would require data match for Loads, are not supported because the LX4580 CPU often resolves Loads for a given context in the background of execution of other contexts.

As noted in Section 2.5.2 only a single context of the LX4580 CPU is allowed to execute in Debug Mode at any given time. Furthermore, if the EJTAG Control Register "Disable Other Contexts" (DOC) bit is set when any context enters Debug Mode, all other contexts suspend execution. As indicated in Table 2 each context has its own CP0 Debug and DEPC registers to provide independent context control of EJTAG and to hold the DEPC for each context that is in DM Wait state. On the other hand, there is only one DESAVE register that is shared by all contexts since it is only needed during execution in Debug Mode.

For both Instruction and Data Breaks, the match logic is extended to include an optional match against the context number.

For EJTAG Breaks, an additional field in the EJTAG Control Register is used to indicate whether all contexts are to be interrupted, or just a specific context is to be interrupted.

#### 2.9. CP0 Hazards

In all cases the implementation meets or exceeds the "typical" requirements for instruction spacing to avoid CP0 hazards as described in the MIPS32 architecture specification.

## 2.10. Performance Counters

The LX4580 CPU implements four performance counters, as noted in Table 2. Each counter can select from the same set of events to count, and each counter can count the selected event for all contexts, or for one particular context. The format of the counters and their control registers follows the MIPS32 Release 2 specification, with one Lexra extension (the CntxSel field) in bits 13:11 of the control registers, as defined in Table 6. The Event field (bits 10:5) of the MIPS32-specified counter control registers is defined in Table 7.

Because there is only one set of performance counters, they are shared by all contexts and it is the responsibility of software to control their use by more than one context, if so desired. One particular aspect of the MIPS32-specified control registers that is specific to the LX4580 CPU is the IE field, which indicates that a Performance Counter Interrupt should become pending under certain conditions. In the LX4580 CPU, *the IE field applies to the context that most recently wrote the control register in question*.

| Value (bits 13:11) | Context to Count              |

|--------------------|-------------------------------|

| 000                | Count Events for all Contexts |

| 100                | Count Events for Context 0    |

| 101                | Count Events for Context 1    |

| 110                | Count Events for Context 2    |

| 111                | Count Events for Context 3    |

| others             | reserved                      |

## Table 6: CntxSel (bits 13:11) Field of PerfCnt Control Registers

#### Table 7: Event Field of PerfCnt Control Registers

| Value (bits 10:5) | Event Counted                         |  |

|-------------------|---------------------------------------|--|

| 000000            | retired instructions                  |  |

| 000001            | replayed instructions                 |  |

| 000010            | instruction fetch (valid new D-stage) |  |

| 000011            | Icache instruction fetch              |  |

| 000100            | Icache miss                           |  |

| 000101            | Uncached instruction fetch            |  |

| Value (bits 10:5) | Event Counted                                |  |

|-------------------|----------------------------------------------|--|

| 000110            | Dcache load <sup>a</sup>                     |  |

| 000111            | Dcache store <sup>a</sup>                    |  |

| 001000            | Dcache load miss                             |  |

| 001001            | Dcache store miss                            |  |

| 001010            | Dcache load or store <sup>a</sup>            |  |

| 001011            | Dcache load or store miss                    |  |

| 001100            | Uncached load or store <sup>a</sup>          |  |

| 001101            | Writeback for replacement                    |  |

| 001110            | Writeback for inquiry                        |  |

| 001111            | Invalidate for inquiry                       |  |

| 010000            | Nop for inquiry                              |  |

| 010001            | Pipeline stall for any reason                |  |

| 010010            | Pipeline stall for Icache fill               |  |

| 010011            | Pipeline stall for Dcache fill               |  |

| 010100            | Pipeline stall for store from store queue    |  |

| 010101            | Pipeline stall for write buffer full         |  |

| 010110            | execution exception (Ov,Trap,BREAK,SYSCALL)  |  |

| 010111            | TLB refill exception - Instruction           |  |

| 011000            | TLB refill exception - Data                  |  |

| 011001            | TLB invalid exception - Instruction          |  |

| 011010            | TLB invalid exception - Data                 |  |

| 011011            | TLB modified exception                       |  |

| 011100            | any TLB exception                            |  |

| 011101            | ITLB miss                                    |  |

| 011110            | DTLB miss                                    |  |

| 011111            | Interrupt                                    |  |

| 100001            | any exception                                |  |

| 100010            | Store Conditional instruction (pass or fail) |  |

| 100011            | Store Conditional Fail                       |  |

| others            | reserved (no count)                          |  |

## Table 7: Event Field of PerfCnt Control Registers

a. Counts replayed and retired versions. The number of replays does not significantly contribute to the overall count.

## 2.11. Release 2 Architecture Support

The LX4580 CPU supports the MIPS32 Release 2 Architecture Changes. Those changes include numerous optional and implementation dependent features as well as several required features. The following sections provide detail on the LX4580 implementation. As a quick summary, the following is a list of all of the Release 2 features and their support in the LX4580 CPU:

| • | Vectored Interrupts                 | (not supported) |

|---|-------------------------------------|-----------------|

| • | External Interrupt Controller       | (not supported) |

| • | Programmable Exception Vector Base  | (supported)     |

| • | Atomic Interrupt Enable/Disable     | (supported)     |

| • | Disable Count register              | (supported)     |

| • | GPR Shadow Registers                | (not supported) |

| • | Field, Rotate, Shuffle Instructions | (supported)     |

| • | Hazard Barrier Instructions         | (supported)     |

| • | User Hardware Register access       | (supported)     |

| • | CP0 register changes                | (supported)     |

| • | 64-bit FPU                          | (not supported) |

| • | 1KB page size                       | (not supported) |

## 2.11.1.Release 2 Interrupt Modes, Exceptions, Shadow GPRs

The Release 2 Architecture defines a Compatibility interrupt mode which is equivalent to the Release 1 interrupt mode. This is the only Release 2 interrupt mode supported by the LX4580 CPU. The Vectored and External Interrupt Controller (EIC) modes are not supported. GPR Shadow Registers are not supported.

As noted in Section 2.4, the Timer and Performance Counter interrupts are presented as IP7. Therefore the IPTI and IPPCI fields of the Release 2 IntCtl register have that value. The other fields of IntCtl are always zero. The Cause register fields TI and PCI are implemented to provide a direct indication of Timer and Performance Counter interrupts. Since EIC mode is not supported, the Status and Cause registers never use the IPL and RIPL formats for interrupt priority levels.

Because there is only a single Count register shared by all contexts, the DC (Disable Count) bit in the Cause register only has an effect if all contexts set their individual DC bit. Otherwise the Count register continues to run.

The Release 2 EBase register is fully implemented. Within the EBase register, the least significant bits of the CPUNum field reflect the context number within the LX4580 CPU. That is, each context reads a unique CPUNum value from its EBase register. There is one EBase register per context so that each can independently set its exception base value.

The Release 2 EI and DI (Enable and Disable Interrupt) instructions are implemented as required.

Because Shadow Register and Vectored Interrupts are not implemented, the SRSCtl register is always read as zeroes and SRSMap is not implemented. Furthermore, the RDPGPR and WRPGPR instructions simply move the contents of one GPR to another within the executing context's GPR register set.

## 2.11.2. Hazard Barrier Instructions

The Release 2 instructions EHB, JALR.HB, JR.HB and SYNCI are implemented by the LX4580 CPU to eliminate execution and instruction hazards as described in the Release 2 Architecture.

One implementation dependent aspect of the SYNCI instruction concerns address exceptions. The LX4580 CPU will *not* take an AdEL for a reference by SYNCI to kernel space while in user mode.

#### 2.11.3. Field, Rotate, Shuffle Instructions

The following Release 2 instructions are implemented as required. It is worth noting that a programming note in the Release 2 specification indicates how the WSBH instruction can be used to swap endianness.

- EXT Extract Bit Field

- INS Insert Bit Field

- ROTR Rotate Right

- ROTRV Rotate Right Variable

- SEB Sign-Extend Byte to Word

- SEH Sign-Extend Halfword to Word

- WSBH Word Swap Bytes Within Halfwords

#### 2.11.4. User Access to Hardware Registers

The Release 2 instruction RDHWR (Read Hardware Register) is implemented as required. The CP0 register HWREna is also implemented as required to conditionally enable a User mode program to read one or more of the defined registers. The values that are supplied when the RDHWR instruction is executed (if the relevant register is enabled for reading) are shown in Table 8.

| Number | Name       | нмт | IT Implementation Specific Information |  |

|--------|------------|-----|----------------------------------------|--|

| 0      | CPUNum     | 4   | Same as CP0 EBASE.CPUNum               |  |

| 1      | SYNCI_Step | 1   | 64                                     |  |

| 2      | СС         | 1   | Same as CP0 Count register             |  |

| 3      | CCRes      | 1   | 1                                      |  |

#### **Table 8: Hardware Register Values**

#### 2.11.5. CP0 Register Changes

All of the changes and additions to CP0 registers that are associated with the Release 2 architecture are reflected in Table 2, "Standard CP0 Registers". Beyond the changes and additions associated with Release 2 features that are described in other sections of this document, a few more CP0 register changes are included in the LX4580 CPU to be compliant with the Release 2 architecture.

In particular, the Config, Config2, and Config3 have a few more fields defined. Since the Config2 and Config3 fields all refer to features that are not supported in the LX4580 CPU, these registers are not implemented.

The optional WatchHI register has some fields added, but since the LX4580 does not implement the Watch registers, these are not implemented.

The PerfCnt control registers have a W-bit added which only applies to MIPS64 implementations and so is always 0 on the LX4580 CPU.

## 2.11.6. 64-bit Coprocessor (FPU)

Since the LX4580 does not support any coprocessors, the Release 2 changes to support 64-bit coprocessors, and in particular a 64-bit FPU, are not implemented. The instructions associated with this Release 2 feature will all take Coprocessor Unusable exceptions as required.

## 2.11.7. 1KB Pages

The Release2 architecture extends the PageMask register by a pair of bits and several other CP0 registers are extended or modified if 1KB pages are to be supported. Also, if 1KB pages are to be supported, a PageGrain register is required.

The LX4580 CPU does not support the 1KB page feature. Therefore, the PageGrain register is not implemented and the changed formats of other registers are not implemented. The extra two bits of PageMask are hard coded to 2#11 as seems to be required.

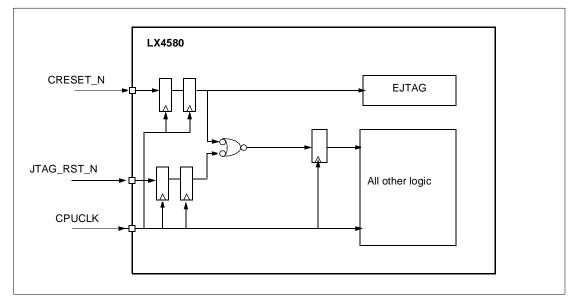

## 3.1. Reset Overview

The LX4580 employs a locally sampled reset strategy - synchronous resets registered at the block level.

#### Figure 2: Reset Overview

The reset strategy ensures the following:

- Complete initialization of the LX4580 by the assertion of one external pin.

- Reset debug by EJTAG. The CPU can be placed in a state whereby they will all receive a debug exception when reset and will fetch their reset vector from EJTAG probe space.

- Reset of flip-flops in multiple clock domains. For this reason reset must remain asserted until it is registered in each domain in the design.

- Due to the synchronous nature of resets all clocks must be running when reset is asserted. This includes external interface clocks.

- When reset is asserted all block-level signals must go to an inert state (e.g. for a bus the arbiter must have grant de-asserted during resets). This allows blocks in different clock domains to come out of reset at different times.

- Two external reset pins are provided for power up and debug reset.

#### 3.2. Reset Distribution

The reset system is distributed across the design. Each block will contains a reset flip-flop which samples the chip-level reset in its clock domain. The output of the reset flip-flop is fed to all the flip-flops in that block.

#### 3.3. Reset Operation

A cold-boot sequence would be as follows:

- 1. CRESET\_N is asserted.

- 2. CRESET\_N is de-asserted.

- 3. Context 0 of the CPU starts executing instructions from the reset vector.

- 4. The software will initialize the multiple context environment and the peripherals.

A typical multiple CPU EJTAG boot sequence would be as follows:

- 1. CRESET\_N is asserted.

- 2. CRESET\_N is de-asserted.

- 3. The EJTAG probe is connected to the CPU in turn setting the ProbeEn bit of the CPU's EJTAG Control Register.

- 4. The Probe then asserts JTAG\_RST\_N. This resets everything in the LX4580 apart from the EJTAG ProbeEn flop.

- 5. JTAG\_RST\_N is de-asserted the CPU jumps to the debug exception vector at 0xFF200200 from where the system is under EJTAG probe control.

## 3.4. Reset External LX4580 Interfaces

#### **Table 9: Reset External Interface**

| Signal Name | Direction | Description                      |

|-------------|-----------|----------------------------------|

| CRESET_N    | input     | Cold Reset.                      |

| JTAG_RST_N  | input     | Connection from the EJTAG probe. |

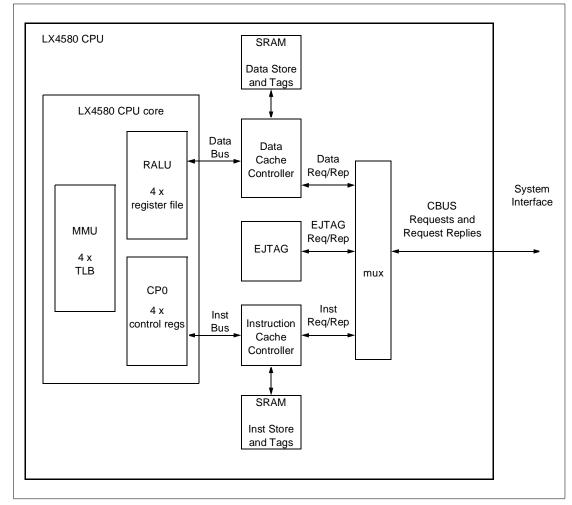

## 4.1. LX4580 CPU Overview

This chapter describes the CPU's caches.

The LX4580 CPU includes the following features:

- 500 MHz operation.

- 7-stage pipeline.

- Supports Release 2 MIPS32<sup>™</sup> instruction set.

- Four hardware contexts with fine-grained Hardware Multi-Threading (HMT).

- 64, 32, or 16 KByte 4-way set associative instruction cache.

- 64, 32, or 16 KByte 4-way set associative writeback, allocate on write, data cache.

- Performance counters.

## 4.2. LX4580 CPU Core

The LX4580 CPU core implements the full Release 2 MIPS32<sup>™</sup> instruction set as described in Chapter 2. The major blocks of the CPU core are the Register file and ALU (RALU), Control Processor (CP0) and

Memory Management Unit (MMU). Architecturally visible registers in these blocks are replicated to provide a separate copy for each of the CPU contexts.

#### 4.3. Instruction Cache

The LX4580 CPU includes a 4-way set associative instruction cache that operates at the processor clock speed. The instruction cache is organized in 64-byte lines, with Valid and Invalid states.

#### 4.4. Data Cache

The LX4580 CPU includes a 4-way set associative data cache that operates at the processor clock speed. Data in the cache is organized in 64-byte lines.

#### 4.5. Cache Line Replacement Algorithm

When a new line must be brought into the instruction cache or data cache, it may be necessary to evict a line that is currently held. The caches use a 2 bit Most Recently Filled (MRF) field to implement the replacement algorithm. This value is stored as an extra two bits in tag 0 RAM and is updated any time fill data is returned to the cache. On a fill, the stored MRF value indicates which way is currently being filled, so at any point in time this value represents the most recently filled line.

When the data cache needs to allocate a location for a new line, it first examines the valid bits of all 4 ways. If any of the 4 ways are invalid, the smallest number way (0->3) that is invalid is selected. If all 4 ways are valid, the way equal to  $((MRF + 1) \mod 4)$  is selected.

The instruction cache does not examine the valid bits in its replacement algorithm. It simply selects the way equal to  $((MRF + 1) \mod 4)$  as shown in the last 4 rows of Table 10.

When the data cache has misses for more than one context to the same cache index, it tracks the replacement Way for each of them and must update the MRF bit in the order that the misses were allocated. When more than one context misses to the same cache index, the instruction cache simply suspends the second context without making a request. After the first miss is resolved, the suspended context resumes execution and (assuming it misses again) then makes its request.

| Tag state                     | MRF | Way selected       |

|-------------------------------|-----|--------------------|

| Way 0 invalid                 | xx  | Way 0 <sup>a</sup> |

| Way 0 valid, Way 1 invalid    | хх  | Way 1 <sup>a</sup> |

| Way 0,1 valid, Way 2 invalid  | xx  | Way 2 <sup>a</sup> |

| Way 0,1,2 valid Way 3 invalid | xx  | Way 3 <sup>a</sup> |

| Way 0-3 valid                 | 00  | Way 1              |

| Way 0-3 valid                 | 01  | Way 2              |

| Way 0-3 valid                 | 10  | Way 3              |

| Way 0-3 valid                 | 11  | Way 0              |

#### Table 10: Cache Line Replacement Algorithm

a. This row does not apply to the instruction cache, which ignores the valid bits in its replacement algorithm.

Within the data cache, lines may be locked using the Load Linked (LL) instruction. When one thread executes an LL, that line is locked until a Store Conditional (SC) instruction is executed or some other operation breaks the lock. (See Section 2.2.1) If a line is locked, it cannot be replaced. If the algorithm above selects a line that is locked, the algorithm will increment the way by 1 (way + 1 mod 4) and choose that way. If that way is also locked the algorithm increments again until it finds a way that does not have a locked line.

## 4.6. CPU Error Handling

## 4.6.1. Bus Error Handling (IBE and DBE)

When a Bus Error is detected, it is reported to the CPU and context associated with the request. Within the CPU the request which caused the Bus Error must have been one of the following:

- Instruction Fetch (cached or uncached)

- Data Access with Response (typically a read or cache fill)

- Data Access without Response (typically a write or eviction)

For an instruction fetch, the Bus Error replaces the response that would have contained the expected data. The context is marked as IBE Pending. The Icache state machine for the context is released (with no change in the cache if the request was a cached instruction fetch). The context is released from its suspended state so that it can take the IBE exception, as described below.

For a data access with response, the Bus Error replaces the response that would have contained the expected data. The context is marked as DBE Pending. The Dcache state machine for the context is released. If a replacement eviction was required, the cache line will be left in the Invalid state. If no eviction was required, the data cache is unchanged. If a GPR was to be loaded with the data, the value of the GPR is unpredictable (writing zeroes or leaving the GPR unchanged would not be any more useful to software). The context is released from its suspended state so that it can take the DBE exception, as described below.